电池知识

锂离子、磷酸铁锂、锰酸锂、新能源

电池知识

锂离子、磷酸铁锂、锰酸锂、新能源

硬软件配合始终都会存在一些冲突,小编偶然发现这篇文章,给大家分享一下这些内容,希望能帮助大家解决一些问题。

一,1,电源线宽度在20mil以上。

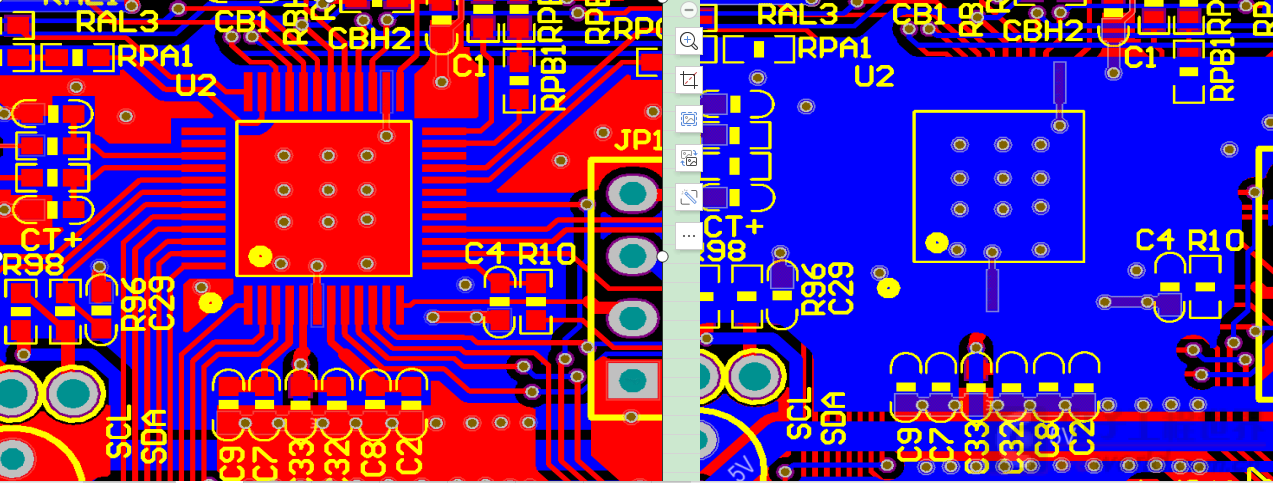

2,芯片背面的最好不要走线,保持地线覆铜的完整性,(参见样例一)。

3,所有信号线必须在经过去耦、滤波电容之后才能进入相应的元器件管脚,不能将去耦、滤波电容放置在一旁。

二,1,AVDD管脚处接一个大于或等于1uF瓷片去耦电容。

2,AVDD管脚到去耦电容之间的距离小于2cm(参见样例一)。

3,AVDD管脚到去耦电容连接线之间没有过孔。

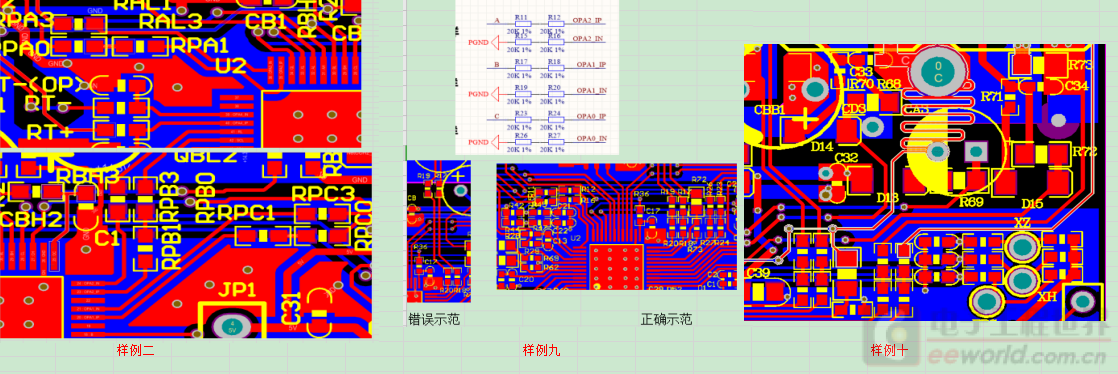

三,1,运放输入端的匹配电阻距离芯片引脚应小于2cm(参见样例二),并且两组电阻不能分开(参加样例九)。

2,运放输入端的匹配电阻连接到相应MOS管源极和漏极(或采样电阻两端)的引线应走差分线,不可以就近选择系统地线(参见样例十)。

3,运放输入端及连接的匹配电阻到最终的采样电阻之间的走线,就尽可能减少过孔的数量(参见样例十)。

四,1,AVDD的去耦电容接地端、RESET的复位电路电容接地端,与芯片的地(AVSS)之间围成的区域是全部覆地(在芯片背面),该区域围成的地没有被其他走线分割(参见样例一)。

2,RESET的RC复位电路距离芯片1cm以内(参见样例一)

3,PCB顶层和底层的覆地,每平方厘米内过孔5个以上(参见样例一)。

4,AVDD/RESET滤波电容的接地端需通过2个以上的过孔打到背面的大面积覆地,芯片地需通过6个以上过孔到背面覆地。

5,开关电源部分不能覆地,大面积敷地和开关电源部分保持至少3mm的距离。

五,1,过孔内径不小于15mil。

2,芯片的所有模拟输入端不能悬空,例如OPA_IP OPA_IN等,不使用时需将其接地。

3,信号线和地线上不可串磁珠。

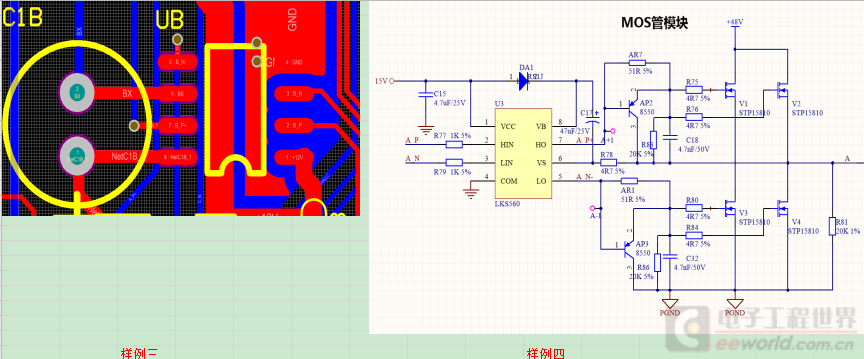

六,1,使用集成预驱动芯片的设计,集成预驱动芯片的GND引脚通过过孔接地的,至少使用两个过孔(参见样例三)。

2,使用集成预驱动芯片的设计,集成预驱动芯片的VCC引脚通过过孔接电源的,至少使用两个过孔。

3,使用集成预驱动芯片的设计,为减少信号反射,预驱芯片的两个输入端需要加一个1K电阻(参见样例四)。

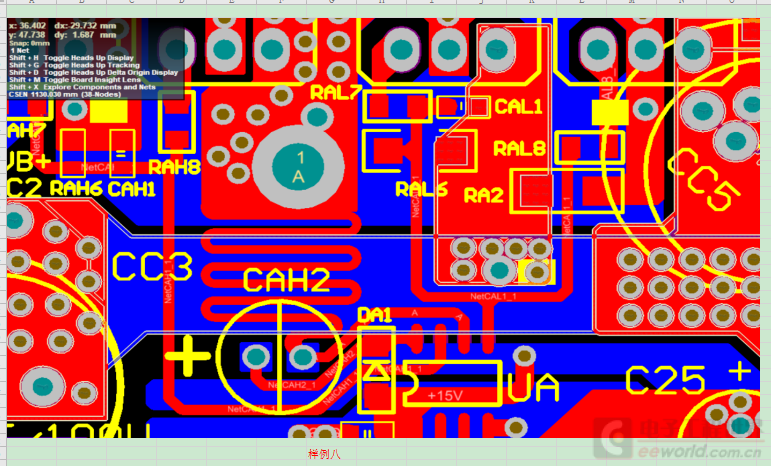

4,预驱芯片的VS端要先经过Boost电容再到相线,PCB上需要走蛇形线,形成一个小电感,用来降低相线较大的dV/dt对预驱芯片的影响(参见样例八)。

声明: 本站所发布文章部分图片和内容自于互联网,如有侵权请联系删除